9.6. Address Translation

- 9. Virtual Memory {CSAPP}

- 9.6.2. Speeding Up Address Translation with a TLB

TLB는 가상메모리를 물리메모리로 변환하는 과정에 매번 Page Table을 참조해야 하는 비효율성을 줄이기 위해 MMU 안에 탑재된 공간을 의미.

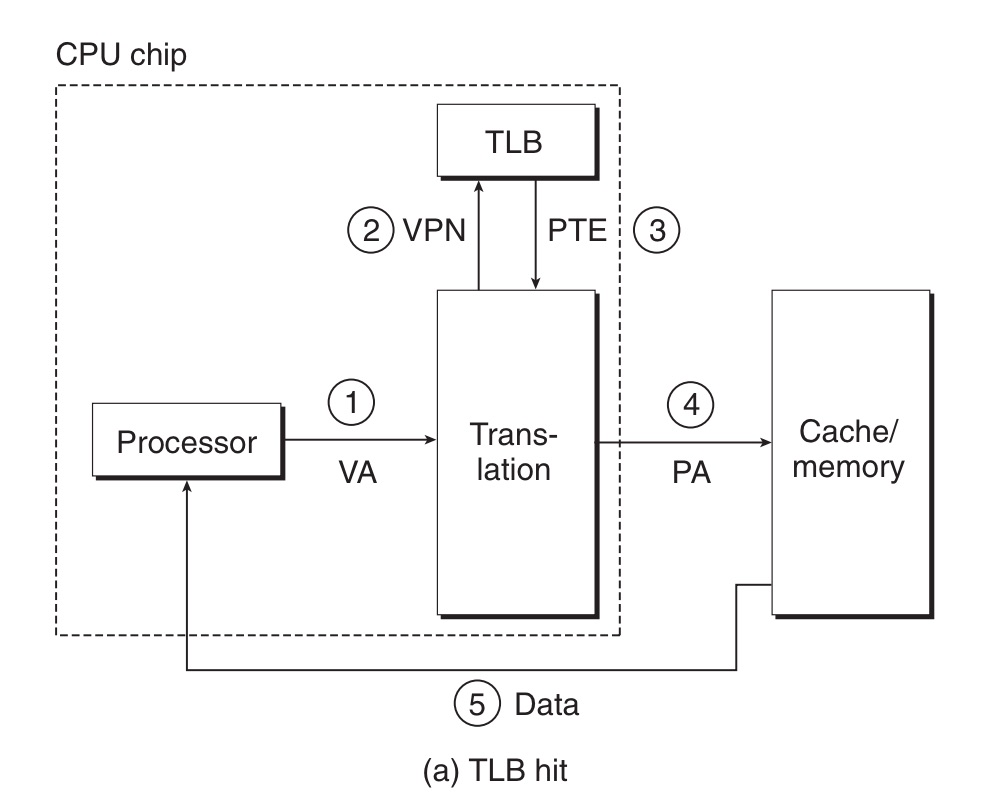

TLB Hit#

- CPU가 VA를 생성한다.

- MMU는 TLB에 VPN(Virtual Page Number)과 연관된 PTE를 쿼리하고

- TLB Hit가 발생하여 PTE 값을 가져온다.

- MMU는 PTE에 들어있는 물리주소의 값을 캐시/물리메모리에 요청한다.

- 캐시/물리메모리는 해당 위치에 들어있는 워드를 CPU에게 반환한다.

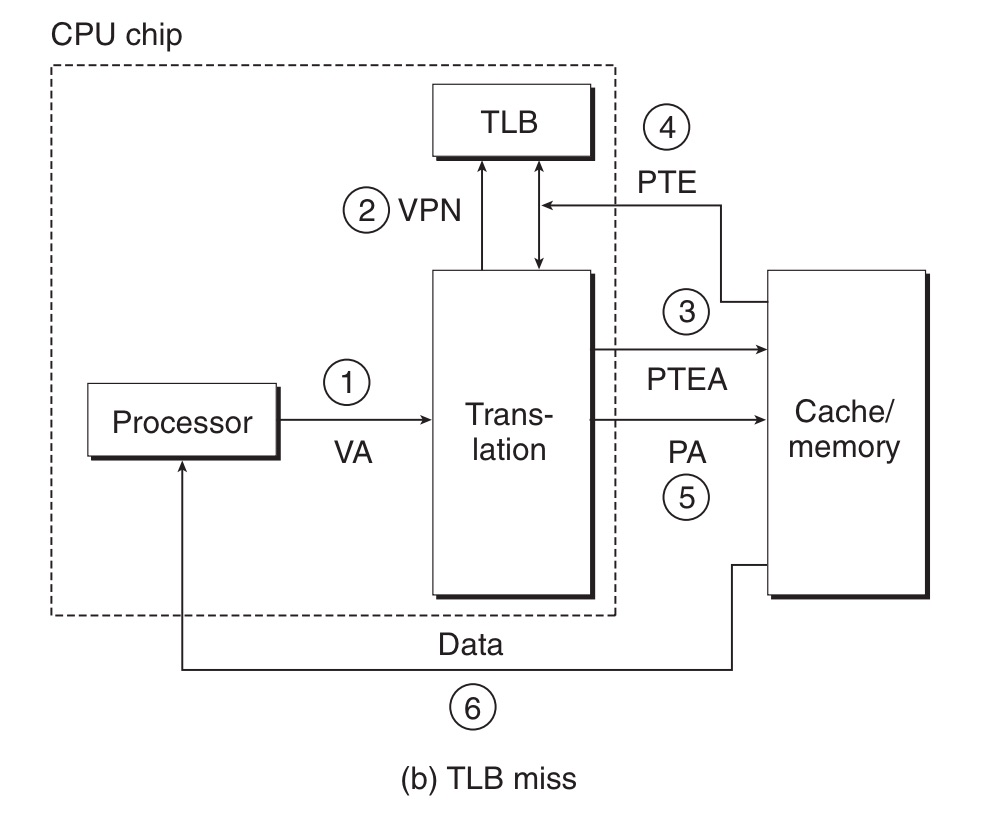

TLB Miss#

- CPU가 VA를 생성한다.

- MMU는 TLB에 VPN과 연관된 PTE를 쿼리하고 TLB Miss가 발생함을 인지한다.

- OS는 인터럽트 핸들러를 호출해 페이지 테이블을 검색하여 Page Table Entry를 구한다.

- 이렇게 구한 PTE는 TLB에 업데이트 된다.

- PTE로부터 물리주소를 알아내 캐시/물리메모리에 요청한다.

- 캐시/물리메모리는 해당 위치에 들어있는 워드를 CPU에게 반환한다.

- OS는 해당 명령을 다시 실행하여 프로세스를 계속 진행한다.

TLB에 Virtual Address를 넣으면 어떻게 Physical Address가 튀어나오나요?#

TLB는 기본적으로 n-way set associative 방식을 사용합니다. VA 하위비트 -> VPN -> TLBI(index)와 TLBT(tag)를 생성합니다. MMU는 TLB의 TLBI번째 인덱스의 TLBT태그에 적혀있는 PPN(Physical Page Number)와 valid 비트를 확인합니다. 이때 valid 비트가 꺼져있으면 MMU는 하드웨어 예외를 발생시키고 켜져있으면 PPN을 곧장 사용합니다.